Why does the JK flip-flop toggles on the 'negative edge' of its clock input when its inputs are connected to +v (i.e when j=1 , k=1)? - Quora

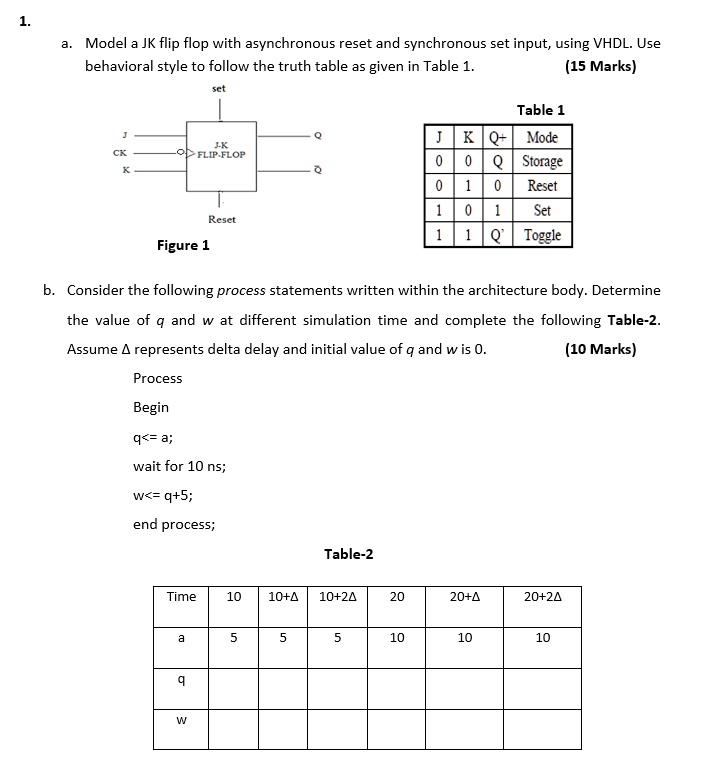

Verilog Coding Tips and Tricks: Verilog Code for JK flip flop with Synchronous reset,set and clock enable

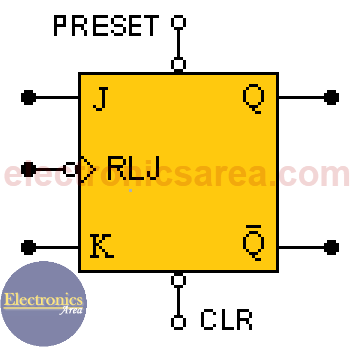

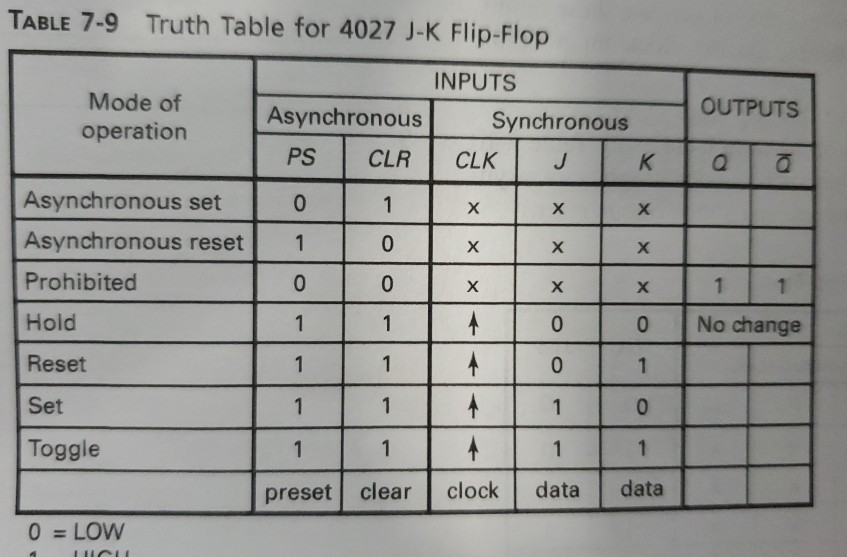

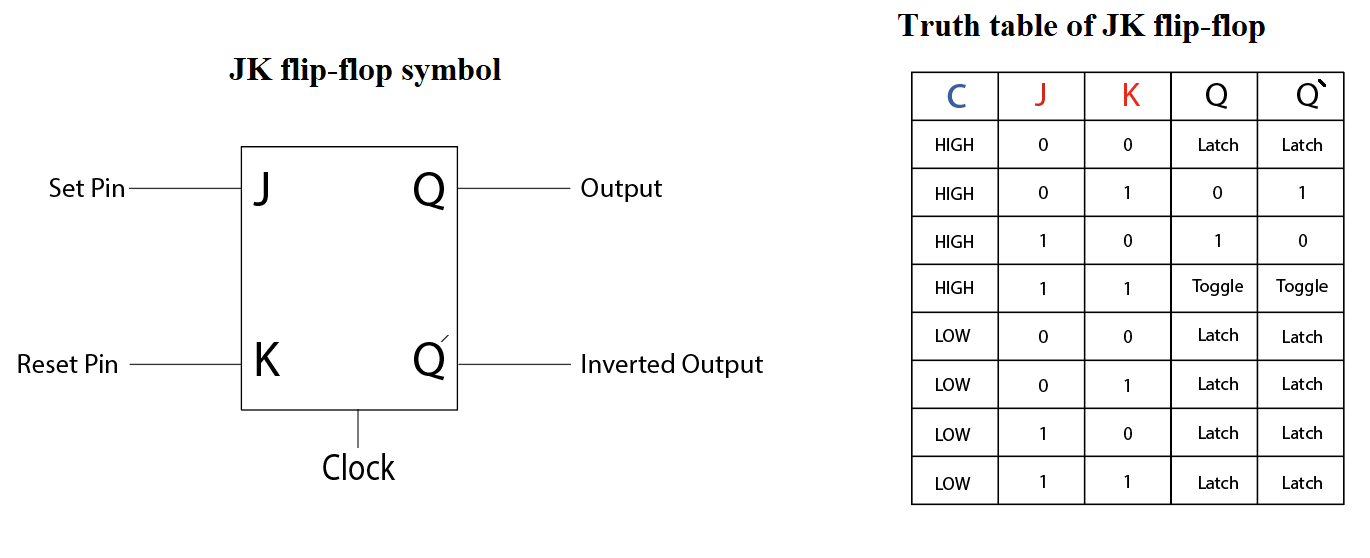

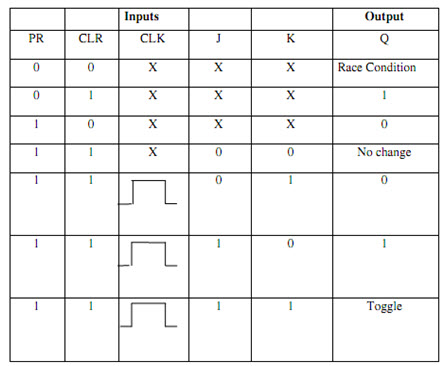

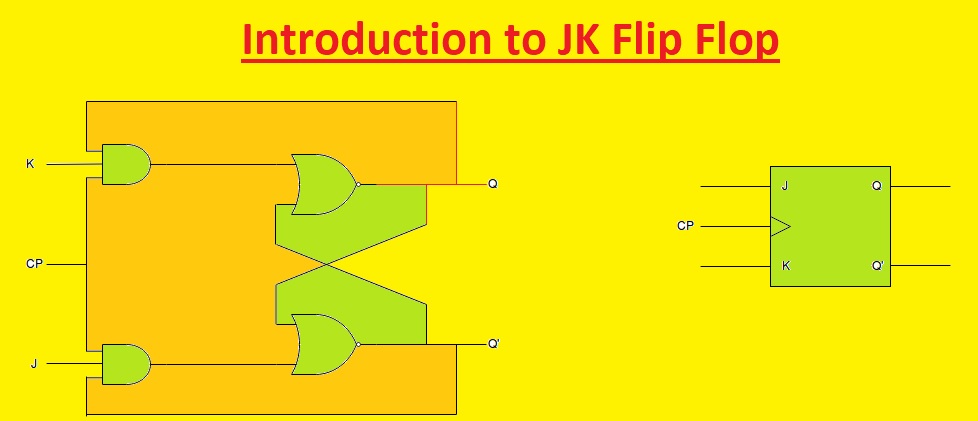

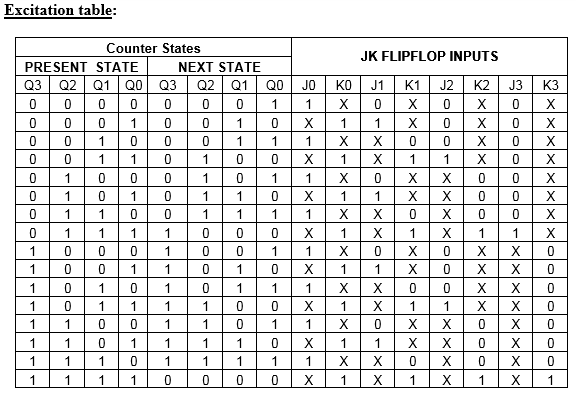

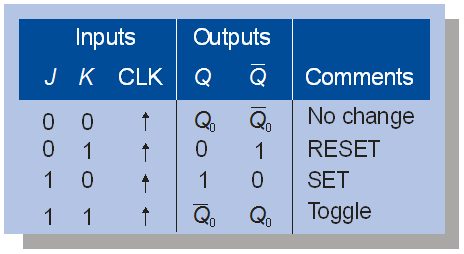

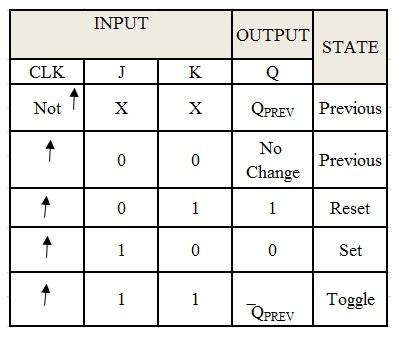

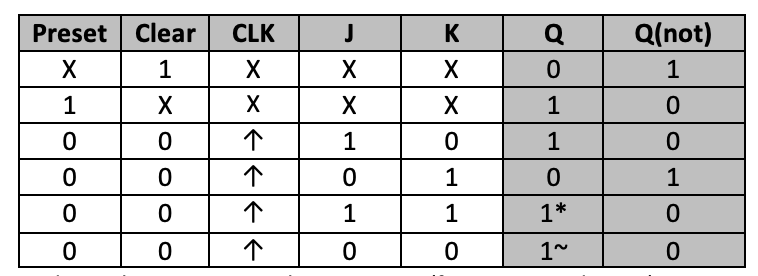

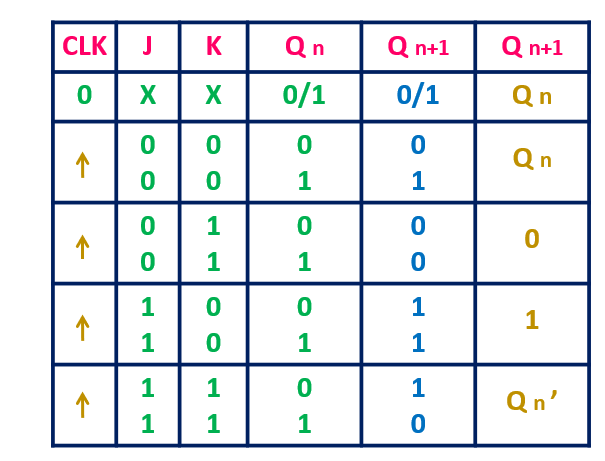

JK Flip-Flop Explained | Race Around Condition in JK Flip-Flop | JK Flip-Flop Truth Table, Excitation table and Timing Diagram - ALL ABOUT ELECTRONICS